1. Overview

In this tutorial, we’ll briefly give details about the pros and cons of the two forms of CPU design, reduced instruction set computing (RISC) architecture, and the complex instruction set computing (CISC) architecture.

2. RISC vs. CISC

The debate of the best way to design a CPU has been continuing since the 80s. Some computer scientists support the idea that low-level instructions should be long and powerful. This can be done by using fewer individual instructions to perform a complex task (CISC). Controversially, some other computer scientists argue that the commands can be shorter and simpler. It requires more individual instructions to perform a complex task (RISC). However, it allows fewer cycles per instructions.

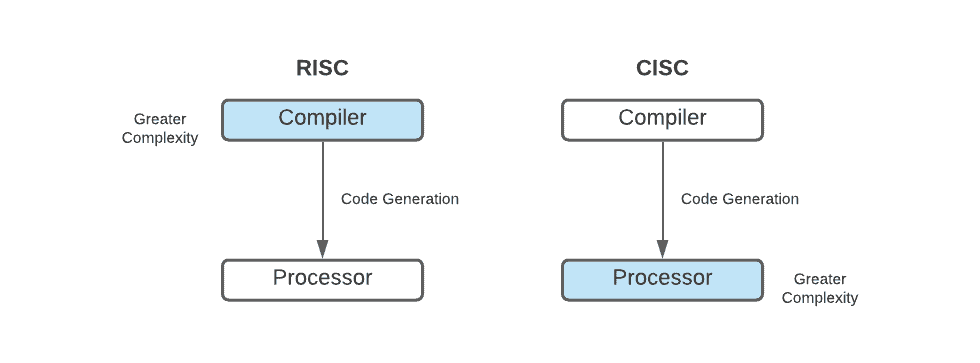

According to Moore’s Law, the number of transistors on a microchip doubles every two years, and the cost is halved. While designing CISC, there is always a high risk because of greater complexity on the hardware side. It also takes more time to design new CISC architecture. On the other side, RISC is a simple architecture and it is simple to implement. It means it takes short time to market and it has a lower risk than CISC. For that reason, RISC is the inevitable conclusion of Moore’s Law.

Even though there are some debates about which one is better, we can say that there is no correct answer for this debate. Because both approaches have advantages and drawbacks. We can see the overall comparison between RISC and CISC in the figure below:

3. RISC

RISC (reduced instruction set computing) architecture is a design choice that aims to reduce the complexity of instructions and to deliver simple but powerful instructions that execute within a cycle at a high clock speed. It is proposed by David Patterson and John Hennessy.

Reducing the complexity of the instruction set performed by the hardware paves the way for providing flexible intelligence by using software rather than hardware. As a result, a RISC architecture design requires greater complexity on the compiler.

3.1. Some Major Design Principles

The RISC has some major design principles:

- Instructions: The number of instruction classes in RISC processors is limited. These classes contain some basic operations that can be completed in a single cycle. The compiler or programmer combines numerous basic instructions to create complex operations such as a division operation.

- Registers: RISC processors have a general-purpose register set. Any register can hold data or an address. For all data processing activities, registers serve as fast memory storage.

- Pipelines: Pipelines divide instruction processing into smaller parts that can be executed in parallel.

- Load-store architecture: The processor works with data stored in registers. Data is transferred between the registers and memory using separate load and store instructions. Since memory accesses are expensive, separating memory accesses from data processing gives a benefit. Because data items can be kept in the register and may be used numerous times without requiring multiple memory visits.

Because of these design principles, RISC processors can be simpler. This situation allows the core to run at higher clock frequencies. On the other hand, traditional CISC processors are more complicated and run at lower clock frequencies. However, the line between RISC and CISC has faded over in recent years. That’s because CISC processors have adopted some of the design principles of the RISC.

The most common examples of RISC are ARM which is used in many cell phones and PDAs, Sparc, and PowerPC.

3.2. Advantages of RISC Architecture

- Because of its simplicity, it provides the use of space on microprocessors as well as energy saving. That’s why it is mostly used in cell phones (ARM processors).

- The RISC architecture contains a set of instructions. This allows high-level language compilers to create more efficient code.

- RISC processors utilize registers to pass parameters and store local parameters.

- RISC instructions use limited arguments. Therefore, it uses a fixed-length instruction. That’s because instructions are easy to pipeline.

- The operation’s speed can be increased while the execution time is reduced.

3.3. Disadvantages of RISC Architecture

- The performance of the RISC processor can depend on the compiler. Because the knowledge of the compiler has a crucial role while translating the CISC code to RISC code.

- It requires so much complexity in the compiler.

4. CISC

CISC is the ancestor approach of CPU design. Because before some principles weren’t found, CISC was prominent in the sector. So, the CISC architecture aims to reduce the number of instructions per program while increasing the number of cycles per instruction.

CISC architecture-based computers are intended to reduce memory costs. Because huge programs require more storage, so large memory causes the cost. to address these issues, the number of instructions per program can be lowered by combining the number of instructions in a single instruction. Therefore it increases the complexity of the instructions on the hardware.

The most common examples of CISC are x86 CPUs.

4.1. Advantages of CISC Architecture

- Since each instruction is complicated, fewer instructions can be utilized to implement a given task.

- It causes small code sizes.

4.2. Disadvantages of CISC Architecture

- In an ordinary process, even though several specialized instructions, in reality, are not even used regularly.

- The machine’s performance will be slowed since the amount of clock time required by various instructions will change.

5. Differences Between RISC and CISC

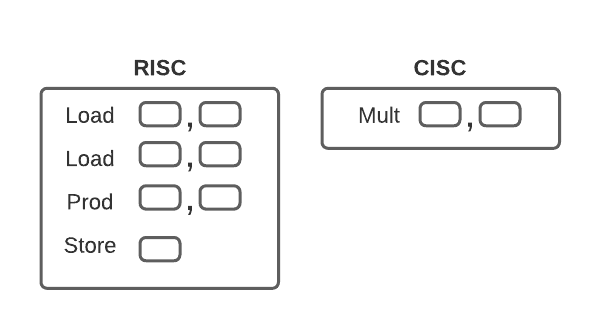

Let’s also look at the figure below to understand the difference between the RISC and CISC. It’s an example of multiplying two numbers in the memory:

In the CISC approach, as we see in the figure, there is only one complex instruction “MULT”. It takes care of everything. It works directly on the memory of the computer. So it doesn’t need the programmer to manually invoke any loading or storing. It is similar to a command in a higher-level language.

In the RISC approach, as we can see in the figure, there is more than one instruction. Because RISC processors execute simple instructions. These instructions can be completed in a single clock cycle. As a result, “MULT” instruction is divided into three separate instructions: “LOAD”, which moves data from the memory to register, “PROD”, which calculates the product of two inputs placed in the registers, and “STORE”, which moves data from registers to memory.

6. Conclusion

In this tutorial, we’ve shared the details of the continuing debate on the design choices of the CPU. We’ve briefly given information about the RISC and CISC architecture. We’ve shared the advantages and disadvantages of both design choices. In recent days, since the ARM is proprietary, RISC-V comes on the stage and starts to change the market share in microprocessor architectures.